TVS Diode Selection & Layout for 24-V Ports | Dual SOT-23 Guide

Dec 12,2025

Preface — Why This Topic Still Matters

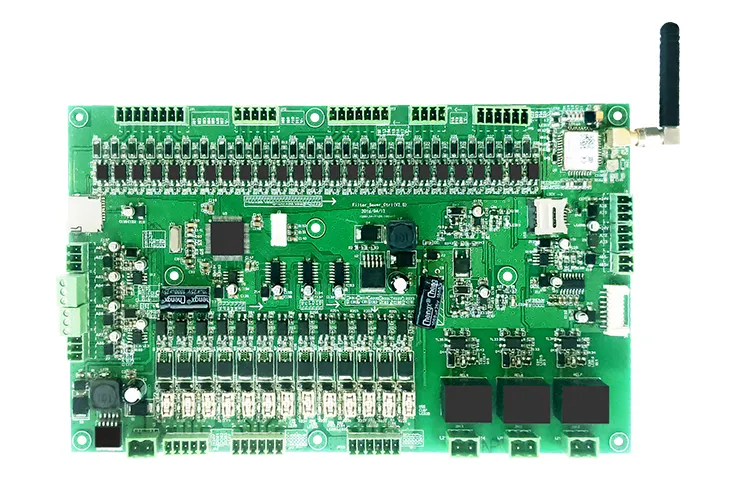

Placed in the preface section, this image aims to visually demonstrate that even with a chosen TVS, design deviations can lead to failures, thereby emphasizing the importance and challenges of reliable transient voltage protection on 24V ports.

Designing for ESD and surge protection often feels like déjà vu for engineers. Yet every year, a new failure case reminds us that even a well-chosen TVS diode can misbehave when voltage tolerance, polarity, or placement are slightly off.

On 24-V industrial ports—found in PLC I/O cards, RS-485 transceivers, or field sensors—the wrong transient voltage suppressor choice can mean marginal compliance or silent degradation after months in the field. This guide collects practical notes from bench experience and design reviews to help you make cleaner, faster, and safer TVS selections for real 24-V hardware.

How do you decide between unidirectional vs. bidirectional TVS?

This image helps engineers understand the fundamental basis for choosing between unidirectional and bidirectional TVS — the polarity of the signal relative to ground. It visually explains why unidirectional TVS is common for DC rails, while bidirectional TVS is needed for AC or differential signal lines (e.g., RS-485).

Choosing between unidirectional and bidirectional TVS diodes is the first real fork in your protection strategy.

A unidirectional device behaves like a zener—it conducts strongly only when the transient exceeds its breakdown voltage in one direction. It’s the go-to for DC rails or single-polarity lines, where ground reference never reverses.

A bidirectional TVS diode, by contrast, uses two opposing junctions in a single body, clamping positive and negative spikes symmetrically. That makes it better for AC or differential lines such as RS-422, RS-485, or CAN.

Most 24-V ports fall into the grey zone: semi-floating references, mixed signal types, and unpredictable surge polarity. In those cases, a bidirectional TVS adds safety margin without extra cost or complexity.

(For related port grounding discussions, see RF connector port placement.)

3-step decision by interface type (DC, single-ended, differential)

A quick 3-step rule of thumb simplifies polarity decisions:

- Check line behavior. If the signal is always positive to ground, a unidirectional part works.

- Look for differential pairs. When two lines swing around a midpoint—like CAN_H/L—use a bidirectional TVS so both sides clamp evenly.

- Review surge path symmetry. On isolated or shielded ports, you can’t always predict polarity, so symmetrical protection avoids one-sided stress.

Lab-level ESD testing often proves this point. Under IEC-61000-4-2 strikes, you’ll notice both line polarities spike nearly equally when a proper bidirectional TVS is in place.

Pitfall: polarity vs. channel count are not the same

It’s easy to confuse polarity with channel count, especially when reading multi-page datasheets.

- Polarity means whether the diode clamps one direction (uni) or both (bi).

- Channel count indicates how many separate lines are protected.

Take NUP2105LT1G as an example: it’s a dual-channel, bidirectional device housed in SOT-23. That means two symmetric clamps sharing one ground return—not two unidirectional parts. Understanding this distinction prevents layout mismatches or reversed footprints during assembly.

Why do 24-V ports benefit from dual-channel SOT-23 TVS (e.g., NUP2105LT1G)?

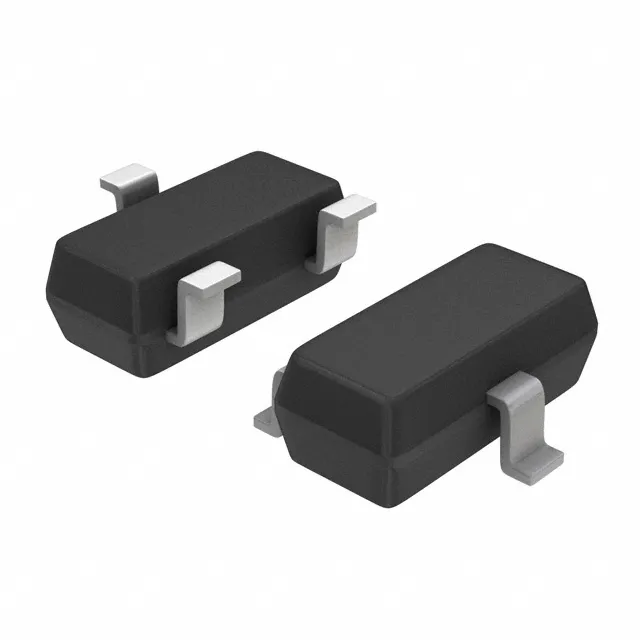

Figure appears in the document as another reliable drop-in alternative. It highlights the features of the onsemi NUP2105L, whose slightly higher reverse stand-off and breakdown voltages (27V / 28V) provide additional design margin against potentially higher voltage transients, suitable for applications with complex power environments or higher robustness requirements.

In compact control modules, space is gold. Dual-channel SOT-23 transient voltage suppressors pack two matched diodes and a shared return path in a 3-pin body.

For 24-V ports—where both signal wires may swing relative to chassis ground—this layout provides balanced surge dissipation and less parasitic skew between the two lines.

The NUP2105LT1G dual bidirectional SOT-23 remains a common favorite: small, inexpensive, and able to sustain the IEC pulse without overheating. Compared with bulkier SMB-type devices, it offers clean routing near connector pins and a compact current return loop, both critical for maintaining signal integrity and EMI immunity.

Pair protection for two-wire/differential lines and return paths

Differential pairs like RS-485 A/B or CAN H/L share one surge destiny—if one wire spikes, the other soon follows. Using a dual TVS ensures they clamp together.

Here’s what you gain:

- Symmetric current flow prevents large common-mode shifts.

- Stable differential voltage protects the transceiver driver pins.

- Matched thermal response reduces drift over multiple ESD hits.

Place the diode right behind the port connector, tie the ground pad to the nearest plane with a short, wide trace, and you’ll contain most surge energy before it leaks deeper into the PCB. This principle mirrors lessons from 50-Ω chain integrity designs in RF circuits—shorter loops always win.

How to size clamp voltage and reverse standoff (V_WM)?

Choosing the right clamp voltage isn’t about going as high as possible; it’s about staying inside the component’s comfort zone.

A proper TVS diode selection keeps your system’s steady-state and transient extremes both within spec:

- V_WM — the maximum DC voltage the diode tolerates without leakage

- V_BR(min) — where conduction begins under rising stress

- V_C(max) — the voltage the diode holds at its rated surge current

Your job: make sure V_WM > V_max (steady-state) and V_C(max) < Abs Max of the protected circuit.

Once both conditions hold, the TVS only reacts when it truly needs to—during transients, not normal operation.

Example math for a 24-V nominal port

Let’s sanity-check a typical case.

A 24-V industrial rail often ranges between 21.6 V (−10%) and 28.8 V (+20%). Suppose the protected IC tolerates up to 40 V absolute max.

Evaluating NUP2105LT1G parameters:

- V_WM = 24 V to slightly above 0.9 × 28.8 V = 25.9 V? Not quite—close enough if the line rarely reaches full tolerance.

- V_BR(min) = 26.2 V to activation begins just past normal operation.

- V_C(max) = 44 V to slightly above the 40 V Abs Max—acceptable if trace impedance or connectors add 1–2 V of damping.

It’s marginal but serviceable, proving why quick margin math beats intuition every time.

Align TVS V_C(max) to the protected device Abs Max

Even short overshoots beyond a pin’s rating can age oxide layers or weaken transceiver junctions. Keep a buffer:

V_C(max) ≤ 0.95 × Abs Max is a reliable rule of thumb.

Too low a V_WM, on the other hand, causes the diode to leak under normal voltage and pollute the signal path. The right part always balances clamp safety and leakage stability—the hallmark of solid ESD protection diode design.

Clamp Fit Calculator

| Parameter | Symbol | Example Value | Check Rule |

|---|---|---|---|

| Nominal Port Voltage | Vnom | 24 V | - |

| Max Tolerance Voltage | Vmax | 28.8 V | - |

| Protected Device Abs Max | Vabsmax | 40 V | - |

| Candidate TVS VWM | VWM | 24 V | Must meet VWM ≥ 0.9 × Vmax |

| Candidate TVS V_BR(min) | V_BR | 26.2 V | - |

| Candidate TVS V_C(max) | V_C | 44 V | Must meet VC ≤ 0.95 × Vabsmax |

| Margin | - | -4 V (40 - 44) | Prefer > 0 V, larger = safer |

Design rule summary:

- If V_WM < 0.9 × V_max to choose a higher standoff part.

- If V_C(max) > 0.95 × V_absmax to move to a tighter-clamp version.

- Otherwise, your device fits safely in the design envelope.

Automating this as a spreadsheet or Python check can save hours during BOM validation or component swaps, especially when cross-referencing suppliers like Digi-Key or Mouser.

Where should the TVS sit on the PCB?

If you’ve ever debugged a failed ESD test, you already know: placement matters more than part number. Even the best transient voltage suppressor will struggle if surge energy has to travel across a long copper trace before reaching it. The goal is to trap the surge where it enters—not let it run through your board first.

In most 24-V port layouts, the TVS diode belongs right behind the connector, ideally within a few millimeters of the exposed pin.

Why? Because the transient’s leading edge travels at nearly the speed of light along the trace. Every centimeter adds inductive impedance and increases residual voltage at your IC.

You’ll often see professional layouts route both signal lines and the TVS’s return path directly to the nearest ground pour. The closer this ground pad sits to the chassis or protective earth connection, the more efficiently it drains ESD current.

Keep-in rules: connector-side placement, shortest loop, ground return

Here’s a condensed checklist that field engineers use when reviewing TVS diode layouts:

- Connector side first. Place the device at the port entry, not mid-trace.

- Shortest current loop. Keep the trace between the connector and TVS under 5 mm if possible.

- Ground via proximity. At least one via per pad, and fan-out to the main plane with wide copper.

- Differential symmetry. For dual TVS packages, route each line equally to avoid skew.

- No unnecessary series elements. Avoid routing surge current through resistors or ferrite beads before the TVS node.

Some designs intentionally add common-mode chokes for noise filtering. In that case, the TVS must sit before the choke—that is, closer to the external connector. If reversed, the choke saturates first and leaves your IC exposed.

These same placement principles appear in many RC snubber for relay/motor damping discussions—shorter, tighter loops reduce overshoot and radiated spikes alike.

Ordering with CM chokes, terminations, RC snubbers

When your port includes additional components—such as termination resistors, common-mode chokes, or snubber networks—the order of placement becomes essential.

The best stack-up from connector inward usually looks like this:

- Connector pin to TVS diode

- TVS node to Common-mode choke (if used)

- Choke output to Line termination or series resistor

- Termination to IC input/output pin

This arrangement ensures that surge energy meets its dissipator (the TVS) first, while slower EMI energy is filtered later.

For low-voltage or RF-sensitive lines, this sequence also minimizes coupling between ESD return currents and high-impedance circuits nearby.

If you notice false ESD test passes that later fail in production, check this order—it’s one of the most common root causes engineers overlook.

Avoid long ground loops and “antenna-effect” traces

Many ESD failures are self-inflicted by ground routing mistakes. A long, skinny ground trace connected to the TVS pad can act like an antenna, radiating energy into nearby nets during an event.

To avoid this:

- Place the TVS ground pad on the top layer close to the connector shield.

- Use multiple vias to stitch to the ground plane—preferably at both ends of the pad.

- Keep the ground return shorter than 10 mm total trace length.

- If space allows, add a small copper pour tying the diode ground directly to chassis for extra current handling.

Also avoid sharp trace corners; at nanosecond rise times, every 90° bend behaves like a mini inductor. Rounded or 45° corners make a measurable difference at ESD’s edge speeds.

Does ~30 pF matter for your signal integrity?

After electrical safety comes the inevitable question: will the TVS diode slow down my signals?

The answer depends on what kind of signal you’re protecting.

A TVS diode such as NUP2105LT1G typically adds about 30 pF of junction capacitance per line. For slow or moderate signals—like GPIOs toggling below a few MHz, relay inputs, or contact sensors—that capacitance is negligible. The signal edges remain clean, and the diode stays effectively invisible.

For faster differential standards such as RS-422, RS-485, or CAN, 30 pF still works if trace impedance is balanced and stub length is short. At data rates under 10 Mbps, the parasitic RC time constant of the diode and line barely dents eye-diagram margins.

However, once your system creeps toward 20–50 Mbps or beyond, that capacitance can start to round signal edges and introduce jitter. It’s here where layout and component choice intertwine.

Impact on RS-422/RS-485, medium-speed GPIO, relay inputs

Let’s break it down by application:

- RS-422 / RS-485 differential pairs:

Place the dual TVS as close as possible to the port. Short traces minimize the apparent capacitance each line sees. A 30 pF diode on both lines forms a balanced load, maintaining impedance near 120 Ω.

- Medium-speed GPIOs or sensor lines:

No real concern. The 30 pF acts as a light filter, even improving noise immunity in long cable runs.

- Relay or opto-isolator inputs:

Capacitance here barely registers, since switching speeds are in the kHz range. What matters more is ensuring the diode can handle surge energy from relay coil kickback—something your system-level RC snubber for relay/motor damping already manages.

The general takeaway: below 10 MHz, 30 pF is harmless; above 20 MHz, verify through simulation or measurement.

When to choose lower-capacitance or single-channel TVS

If you’re pushing into higher data rates—CAN FD, LIN, or low-voltage differential signaling (LVDS)—a 30 pF diode might introduce timing skew. In that case:

- Switch to low-capacitance ESD protection diodes rated around 5–10 pF.

- Use single-channel TVS parts to isolate each line and minimize parasitic coupling.

- Keep pad length short and back-match trace impedance to restore eye pattern integrity.

Low-capacitance devices usually trade surge power for speed. They survive smaller ESD pulses (100–150 W instead of 350 W), but for low-energy interfaces like USB 2.0 or Ethernet PHY inputs, that’s often enough.

The art of ESD protection lies in knowing your worst-case waveform: is it a high-energy industrial surge or a low-energy fast edge? Matching diode specs to that reality ensures reliability without over-engineering.

What changed in IEC 61000-4-2 / -4-5 in 2025?

This image illustrates the practical impact of the 2025 IEC standard update: although the test voltage levels remain unchanged, the stricter waveform calibration means that the protection loop in designs (including TVS placement and grounding) must be more optimized. Otherwise, previously "marginally passing" designs may risk failure under the new standard's tests.

Every few years, the ESD and surge standards evolve—not by changing test voltages, but by tightening how those voltages are verified.

The IEC 61000-4-2:2025 and IEC 61000-4-5:2025 editions (Ed.3) did exactly that. While ±8 kV contact and ±15 kV air levels stay the same, calibration tolerances have narrowed, and waveform verification is now stricter.

That means your next certification test might produce slightly higher residual voltages if your grounding or TVS diode placement isn’t optimized. The standard now focuses on energy equivalence, ensuring every ESD gun or surge generator delivers a consistent pulse shape and rise time.

If your design previously “just passed,” it’s worth a retest under the new Ed.3 procedures.

How do I lock down NUP2105LT1G in my BOM?

After compliance testing, freeze the protection choice.

The NUP2105LT1G remains a trusted dual bidirectional SOT-23 TVS diode for 24-V industrial ports. Here’s a recap of its validated specs:

- V_WM: 24 V

- V_BR(min): 26.2 V

- V_C(max): 44 V

- Surge rating (8/20 µs): 8 A per line

- Peak power: 350 W

- Capacitance: ≈30 pF

- Configuration: Dual, bidirectional, common-cathode

- Package: SOT-23

Before release, confirm availability through DigiKey or Mouser Electronics, and document your validation data—the measured clamp waveform at rated surge, not just the datasheet values.

That one scope capture could save a redesign if future batches show variation.

Trade-offs vs. alternative footprints or single-channel parts

Different footprints solve different problems:

- SOT-23 (dual): Best density-to-power ratio, easy routing, ideal for 24-V differential pairs.

- SMB/SMC packages: Handle >600 W surges, suited for power rails, not fine-pitch signals.

- SOD-923 / SOD-523: Tiny, low-capacitance, but limited to small ESD currents (<100 W).

For most industrial I/O ports below 8 A surge energy, the SOT-23 class provides a safe balance of thermal capacity and placement proximity.

And as always—trust the oscilloscope. Watching your transient voltage suppressor conduct in real-time says more than comparing part numbers.

Should I track 2025 product/news trends?

Yes, especially if you’re designing for the next hardware generation.

Kinetic Technologies announced active-clamp ICs for USB-PD and high-power Type-C ports—devices that monitor line current and dynamically engage a silicon clamp.

These new chips demonstrate a shift toward intelligent surge protection that complements traditional TVS diodes, not replaces them.

Meanwhile, ROHM introduced new automotive TVS arrays with ultra-low capacitance for high-speed CAN-FD and LIN buses. The goal: meet stricter EMC standards without degrading data eye diagrams.

Following such developments helps you design future-proof footprints that accept both passive and active protection variants.

FAQ

Q1. What if my 24-V port occasionally rises to 30 V?

You’re close to exceeding V_WM. Move up one voltage grade—say, to 26 V V_WM—or add a small pre-regulator.

Never rely on the TVS diode to “carry” normal voltage beyond its rated working point; it will overheat and degrade over time.

Q2. How do I calculate the right clamp voltage and working voltage (V_WM)?

Match V_WM ≥ 0.9 × V_max to prevent leakage and V_C(max) ≤ 0.95 × V_absmax to protect ICs under surges. Use the “Clamp Fit Calculator” as a quick design rule check.

Q3. Does a 30 pF TVS degrade RS-485 signal integrity?

Not in most cases. Up to 10 Mbps, a 30 pF ESD protection diode is effectively invisible.

Beyond 20–50 Mbps, check eye diagrams—parasitic capacitance can round edges. For high-speed lines, use low-cap (<10 pF) single-channel parts.

Q4. Where exactly should the TVS be placed—at the connector or near the IC?

Always near the connector, within a few millimeters. The diode’s job is to shunt energy before it travels into the board.

You can add a secondary clamp near the IC only for ultra-sensitive nodes, but the primary protection must intercept the surge at the entry point.

Q5. Can I pass IEC 61000-4-2:2025 compliance with only a TVS diode?

Not reliably. The TVS diode is your first defense, but you’ll also need controlled grounding, shielding, and sometimes common-mode chokes.

Under Ed.3 calibration, weak grounding can cause failure even if the diode spec looks strong. Design the entire return path, not just the component.

Q6. When is a dual-channel SOT-23 better than two singles?

Use dual-channel packages when both lines share a short common return—typical of differential ports.

Separate singles if your layout forces long or asymmetric traces; otherwise, one diode will trigger sooner, unbalancing the protection.

Final Thoughts

Good surge design is less about luck, more about geometry and margin.

By aligning your TVS diode parameters with system limits, respecting IEC return-path physics, and validating under combined ESD + surge conditions, you’ll ship boards that survive both the lab and the field.

It’s the kind of quiet reliability that customers never notice—and that’s exactly the point.

Bonfon Office Building, Longgang District, Shenzhen City, Guangdong Province, China

A China-based OEM/ODM RF communications supplier

Table of Contents

Owning your OEM/ODM/Private Label for Electronic Devices andComponents is now easier than ever.